June 6, 2018

By: Michael Feldman

At this month’s ISC High Performance conference, representatives from Intel, NVIDIA, Xilinx, and NEC will speak about the challenges they face as applications like machine learning and analytics are demanding greater performance at a time when CMOS technology is approaching its physical limits.

The four vendors will make their presentations during a 90-minute focus session called Pushing Digital Computing to the Limits, in which each representative will outline their company’s strategy to advance their processor platforms over the next 12 years. During this period, Moore’s Law, the observation that transistor size and density doubles every couple of years, will slowly come grinding to a halt.

The session will be led by Andreas Stiller, a veteran tech journalist who has covered processor hardware and technology for more than 30 years. Now mostly retired, Stiller continues to work as a freelancer and chairs conference sessions when the opportunities arise. We recently spoke with him to get his thoughts on where the chip industry is headed, especially as it relates to high performance computing, and what it means for the industry.

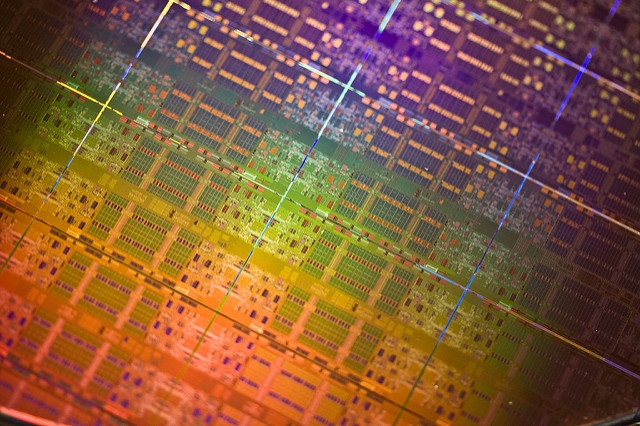

When talking with Stiller, one thing that becomes apparent is that he seems more optimistic about the longevity of silicon-based semiconductor technology than your average industry watcher. “I really see classical CMOS silicon for the next 20 or 25 years,” he says. Stiller thinks the underlying technology will still be practical until we reach transistor geometries in the 1.5nm range.

Beyond that, he says, the silicon-based lattice structures simply won’t support electron flow. Chipmakers could perhaps squeeze another half nanometer or so with more exotic materials like molybdenum compounds and carbon nanotubes, but in short order, they will bump up against their own physical limits.

That’s the good news. The bad news is that we won’t get to enjoy such 1.5nm transistors until around 2030. That’s because the increasing difficulty of shrinking transistors is slowing the rate of Moore’s Law. Thus, instead of going from 10nm to 7nm in one jump, chipmakers like Intel are looking to develop multiple iterations of the same node (i.e., 10nm, 10nm+, 10nm++) over the same timefram, with each version incorporating additional refinements, but with more or less the same transistor geometry.

That has real ramifications for the industry. For example, the delay of Intel’s 10nm technology, which was originally scheduled for 2015/2016, has now been pushed all the way into 2019 for volume production. That delay probably had a role in dooming the “Knights Hill” Xeon Phi processor and likely the entire product line. The abandonment of Knights Hill resulted in the cancellation of the Department of Energy's original Aurora supercomputer, which will reappear in exascale form in 2021 with yet-to-be-determined processors.

When chipmakers can no longer count on better price-performance and performance-per-watt every two years by shrinking transistors, they need to do something else. In general, that something else means relying a lot more on design improvements. Of course, such improvements were always integral to processor design, but without the additional performance of moving to the next process node, architectural innovation becomes much more critical.

One indication that Moore’s Law, and to an even greater degree, Dennard scaling, are no longer driving processor advances, is the growing importance of alternative chip architectures like GPUs and FPGAs. The fact that vendors like NVIDIA and Xilinx literally have a place at the table in Stiller’s session alongside traditional chipmakers like Intel and NEC, is a reflection of the breakdown of these fundamental trends.

Stiller has become particularly interested in a new FPGA design Xilinx recently announced, which they call their adaptive compute acceleration platform (ACAP), which is a completely heterogeneous design that employs an FPGA fabric linking distributed memory, programmable DSP blocks, a multicore SoC, and one or more programmable compute engines, all connected via an on-chip network. Xilinx is promising performance and performance-per-watt that is “unmatched by CPUs or GPUs.” Xilinx CTO Ivo Bolsens plans to elaborate on the ACAP technology during his talk at the ISC session.

NVIDIA has perhaps benefited most from the declining fortunes of transistor shrinkage. The highly parallel architecture of the GPU has turned out to be a particularly good match for applications like machine learning and other types of advanced analytics. Since such a design is inherently less reliance on fast transistors, the company has carved out a sweet spot for itself, especially in the HPC and AI markets. Steve Oberlin, former Cray engineer and now CTO for NVIDIA’s Tesla business, will speak about his company’s plans to evolve their GPUs into the next decade. Maybe he'll even offer some hints about the company's post-Volta architecture.

Meanwhile NEC is looking to make a comeback with its latest vector processor, the SX-Aurora TSUBASA. Once thought too specialized, NEC is hoping the vector platform will get new life in a post-Moore’s Law world. Given the inherent performance advantages of this architecture for HPC codes, vector chips may indeed become more attractive as semiconductor advances become less of a factor. Rudolf Fischer, who heads up the HPC technology group in Europe, will make the case for the future of vector processors.

Given Intel’s current dominance of the HPC market with its Xeon processors, the company is the elephant in any room where processor technology is the topic. During the session, Al Gara, who was the chief architect at IBM in charge of the Blue Gene platform and now occupies a similar position in Intel’s Data Center Group, will speak to the future technologies the chipmaker will bring to bear on the HPC market. Stiller is hoping (as are we) that Gara will elaborate on how the company plans to heal the Xeon/Xeon Phi divide as it moves its datacenter silicon into the exascale era.

Unfortunately, no one from OpenPower or ARM will be present to represent those two architectures. The 90-minute time allotment for Stiller’s session isn’t long enough to encompass the current level of chip diversity in the HPC chip space.

In addition, there will be no advocates for more exotic platforms like quantum, neuromorphic, and optical processors, all of which offer compelling alternatives for HPC work. Stiller expects each of these will come into play over the next 10 to 15 years, and of these, he thinks quantum computing offers the most exciting prospects. That said, he believes none of them will replace conventional digital processors any time soon. “For the foreseeable future,"he says, "we’ll still have CPUs and GPUs."

For those attending ISC High Performance in Frankfurt Germany this month, this session will take place on Tuesday, June 26, from 8:30am to 10:00am, in the Panorama 2 room of Frankfurt Messe.