Feb. 14, 2018

By: Michael Feldman

The Gen-Z Consortium has released Gen-Z Core Specification 1.0, clearing the way for chip vendors, device makers, and switch manufacturers to develop products based on the new standard.

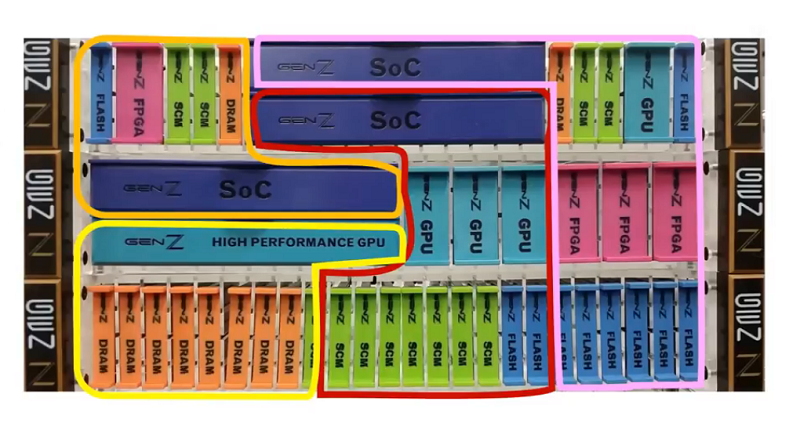

In a nutshell, the technology was devised to provide a standard high-performance, low latency fabric that can tie together processors, main memory, accelerators and storage-class memory. It’s the latter two that provided the major impetus behind Gen-Z. In particular, the sluggish evolution of the PCI- Express standard and the inability of that technology to keep pace with the data speeds of high-performance devices – SoCs, GPUs, FPGAs, and solid state devices, primarily – has created an opening for a new kind of system bus, and one that glue all these components together in creative ways.

Although fabrics such as NVLink, CAPI, and OpenCAPI, are attempting to address some of these same issues, they are largely driven by specific vendors, in those instances, NVIDIA and IBM. The Gen-Z consortium, on the other hand, currently boasts 52 members, including chip vendors AMD, Cavium, Xilinx, and IBM, major server vendors such as HPE, Dell EMC, and Lenovo, and network providers like Mellanox and Broadcom. Intel and NVIDIA are conspicuously absent.

Gen-Z provides something akin to a hybrid fabric, combining a memory bus, a processor bus, a peripheral device bus, and a network interconnect. It also represents a paradigm shift in the way systems access memory. The technology abstracts the underlying media such that processors and coprocessors can access DRAM (like DDR and GDDR), solid data drive memory (like NAND) and storage-class media (like 3D XPoint) with the same protocol.

This decoupling will enable a lot more flexibility in system design and thus, theoretically, encourage more innovation from both OEMs and component providers. It also should make it easier for system software to deal with the kinds of memory-centric architectures that HPE, IBM, and other system vendors are starting to envision.

Performance-wise, there’s also plenty to like. The initial specification supports up to 56 GT/sec, with 112 GT/sec on the immediate roadmap. Memory latencies are in sub-100 ns territory. Point-to-point data transfer efficiency can reach as high as 93 percent when shuttling 256 bytes at a time, dropping to a still-respectable 80 percent for 64-byte transfers. Switch-based transfers are somewhat less efficient.

Despite the broad reach of the Gen-Z consortium, there’s no guarantee that its member will develop products supporting the protocol anytime soon. With new interconnect technologies, it’s something of a chicken-and-egg problem since both the processors and the peripheral devices must support the protocol in tandem. The earliest we can expect products incorporating Gen-Z controllers is probably 2019 or even 2020.

If your interest is piqued, the 1.0 specification can be downloaded here.